# Application of the Plasma Etching technique to Fabricating a Concave-type Pt Electrode Capacitor

# Hyoun Woo Kim and Woon Suk Hwang

School of Materials Science and Engineering, Inha University 253 Yong Hyeon Dong, Nam Gu, Incheon 402-751, Korea

We have used a plasma etching method in order to develop a concave-type Pt electrode capacitor to overcome the limitation of conventional stack-type capacitor in a small critical-dimension (CD) pattern. We have deposited Pt layer on the concave-type structure made by patterning of SiO<sub>2</sub> and subsequently we separated the adjacent nodes by etch-back process with photoresist (PR) as a protecting layer.

Keywords: Pt, Etching, concave, CD.

#### 1. Introduction

In order to increase the storage capacity per cell for 4 Giga-bit dynamic random access memory (DRAM) and beyond, the usage of barium strontium titanate (BST) capacitor has been considered. As an electrode material for BST capacitor, various materials such as platinum (Pt), iridium (Ir), ruthenium (Ru), and ruthenium oxide (RuO<sub>2</sub>) have been studied. Among them, Pt is most appropriate because of its good oxidation-resistance, high electrical conductivity, and low leakage current characteristics. <sup>1),2)</sup>

In order to use the Pt as an electrode material in the stacked capacitor cell structure successfully, Pt etching technique, in order to pattern the bottom electrode, has been developed. However, as Pt has a low reactivity and its etching products have low vapor pressures, he etching of Pt proceeds by physical sputtering. Accordingly, Pt has a low etch slope and thus, as the adjacent nodes are connected with Pt, the bottom Pt storage nodes cannot be separated from their adjacent storage nodes especially in a very low critical dimension (CD) pattern.

In order to allow for lateral shrinkage of the cell sizes while keeping the required cell capacitance without employing the difficult Pt electrode etching, we have developed a concave-type cell structure,  $^{12)}$  revealing that the above method is suitable for the storage node pattern in the CD of 0.17  $\mu$ m and below.

### 2. Experimental

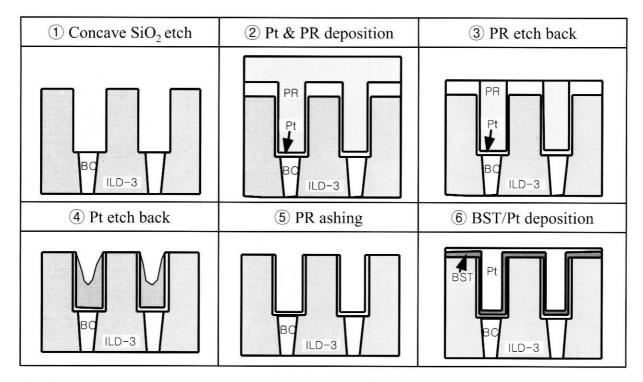

The fabrication sequence of concave-type Pt/BST/Pt capacitor is shown in Fig. 1. After forming a concave

structure with SiO<sub>2</sub>, the bottom electrode Pt layer is deposited. The protective photoresist (PR) layer is deposited, and then the etch back is performed to isolate the Pt layer of each concave structure. After removing the remained PR by ashing, BST and the top electrode Pt layer are deposited to form a capacitor.

The schematic of a reactive ion etcher (RIE) used in this work is shown in our previous work. 12) The combination of high-radio-frequency power (HRF), 13.56 MHz and low-radio frequency power (LRF), 450 kHz, in addition to the low operating pressure (<10 mTorr) results in high-energy ion bombardment. The SiO<sub>2</sub> etching was performed to make a concave structure and a mixture of Ar, CF<sub>4</sub>, and CHF<sub>3</sub> gas was used as an etchant. In the Pt etchback process, the Ar gas and Cl<sub>2</sub> gas were employed as an etchant. In the photoresist etchback process, the O<sub>2</sub> gas was used as an etchant.

### 3. Results and discussion

We have fabricated the etching profile of the concave structure in a pattern with a CD of  $0.17~\mu m$ , using the Ar/CF<sub>4</sub>/CHF<sub>3</sub> plasma (not shown here). The SiO<sub>2</sub> to PR etch selectivity increases by increasing CHF<sub>3</sub> gas flow rate, regardless of HRF power and pressure. The SiO<sub>2</sub> to PR etch selectivity increases by increasing HRF power, regardless of the CHF<sub>3</sub> gas flow rate and pressure. Since the high SiO<sub>2</sub> to PR etch selectivity is crucial for obtaining a vertical profile with a high aspect ratio, we have used an etching condition with a HRF power of 700 W, a LRF power of 0 W, a CHF<sub>3</sub> flow rate of 90 sccm, and a pressure of 70 mTorr, resulting in the SiO<sub>2</sub> to PR etch selectivity

Fig. 1. The fabrication sequence of concave-type Pt/BST/Pt capacitor (ILD-3 represents the interlayer dielectrics of SiO<sub>2</sub> and "BC" represents the buried contact).

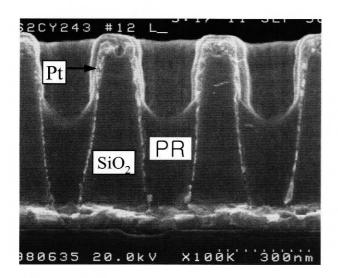

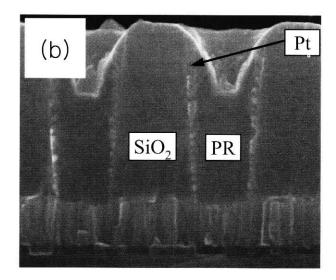

Fig. 2. Concave-type structure (a) before and (b) after the etchback of photoresist (PR) layer.

of 2.4. In order to evaluate the effect of LRF power, we have changed the LRF power from 0 W to 200 W, with an HRF power of 700 W and a pressure of 70 mTorr. The  $SiO_2$  to PR etch selectivity decreases by increasing the LRF power from 0 W to 200 W.

After forming the concave-type structure by etching SiO<sub>2</sub> layer, we deposit the Pt layer which is used as the

bottom electrode of capacitor. On top of it, we coat the PR layer to protect the underlying Pt layer. Since only the Pt layer inside the hole of the concave structure is utilized as the bottom electrode, the coated PR layer and subsequently Pt layer outside the hole needs to be removed. For our etchback process, the chamber pressure was 30 mTorr and the O2 gas flow rate was 50 sccm, with the HRF (13.56 MHz) power and the LRF (450 kHz) power of 600 W and 0 W, respectively. The resulting PR etch rate and etch uniformity are about 6200 Å/min and less than 5 %, respectively. Fig. 2 shows the profiles of the concave-type structure after the etchback of PR layer. We reveal that the Pt layer outside the concave hole is slightly exposed after the etchback process and the Pt layer is not eroded due to the sufficiently high (~ 30 mTorr) etching pressure and resulting low Pt etch rate.

The height of the remaining PR inside the concave hole should be optimized. If the height is too high, some concave holes will have an unwanted PR layer on top of the Pt layer outside the hole. If the height is too low, the PR layer protecting the bottom Pt electrode may be completely eroded during the following Pt etchback process and the bottom Pt layer will be damaged.

In order to separate the Pt layer inside each concave hole and to form a bottom electrode, we remove the Pt layer deposited outside the concave hole by etchback

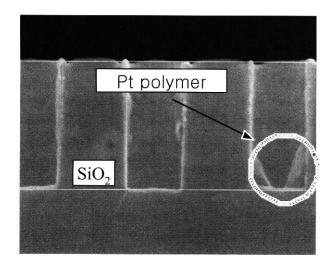

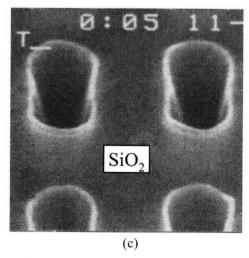

**Fig. 3.** Pt polymer is generated on the bottom of the hole by the excessive etching of Pt.

process. We etched the Pt, PR, and SiO<sub>2</sub> layer concurrently and etched up to the point where the height of the etched SiO<sub>2</sub> layer is about 80 % of the original height.

In our experimet, we observe the air pockets inside the PR in the concave hole. The presence of air pockets will promote the erosion of PR and thus, the bottom Pt layer inside the hole will be exposed. Fig. 3 shows that the Pt polymer is generated on the bottom of the hole by the unwanted etching of the Pt. Since this generated Pt polymer cannot be removed during the following ashing and strip process and thus, disable the bottom Pt electrode, we suggest that the PR layer should be deposited without generating the air pockets inside. Since the generation of the air pocket is related to high revolution speed of PR coater, we are developing a technique to use low-viscosity photoresist without sacrificing the deposition uniformity.

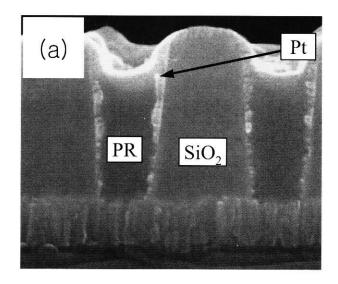

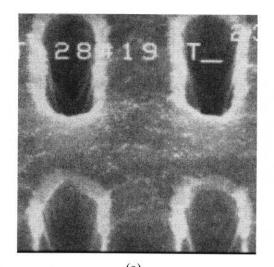

In this step, the Pt to PR etch selectivity needs to be sufficiently high, otherwise the PR layer inside the hole will be eroded away. Fig. 4 shows the change of the profiles depending on the etchback condition with varying process variables. The etching pressure is set to 5 mTorr, because the Pt is mainly etched by physical sputtering and thus, the high pressure reduces the Pt etch rate. When the LRF power is 0 W and the Ar and Cl<sub>2</sub> gas flow rates are 20 sccm and 5 sccm, respectively, the Pt to PR etch selectivity is 1.9 (Fig. 4 (a)). However, if the Pt to PR etch selectivity is relatively low (Fig. 4 (b)), the excessive erosion of PR inside the concave hole is observed.

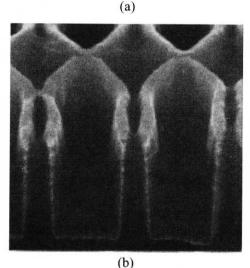

After the Pt layer outside the concave hole is removed and thus, the bottom electrodes are separated, we add an overetch step in considering the etch uniformity. Fig. 5 (a) shows the profile after the just-etch process. Fig. 5

**Fig. 4.** Change of the profiles depending on the etchback condition. (a) The Pt to PR etch selectivity is about 1.9. (b) The Pt to PR etch selectivity is low.

(b) shows the profile using an overetch step of the same recipe as the mainetch step, revealing that the SiO<sub>2</sub> between the nodes are excessively etched. Therefore, we have used an overetch step with HRF power and LRF power of 600 W and 100 W, with a pressure of 30 mTorr, and with Ar and Cl<sub>2</sub> flow rates of 20 sccm and 10 sccm, respectively. In this overetch process, the etch rates of Pt, SiO<sub>2</sub>, and PR are about 1000 Å/min, irrespective of etching material. Fig. 5 (c) reveals the SiO<sub>2</sub> between the nodes are not eroded excessively, and the surface of SiO2 is relatively smooth. After completing the Pt etchback process, we remove the remaining PR inside the concave

**Fig. 5.** Change of the profiles depending on the overetch condition. (a) After just-etch process. (b) After the overetch process with a SiO<sub>2</sub> to Pt etch selectivity of less than 1. (c) After the overetch process with a SiO<sub>2</sub> to Pt etch selectivity of about 1.

hole, and subsequently deposit the BST layer and the top electrode Pt layer, forming the capacitor structure.

#### 4. Conclusions

We suggest to introduce a concave-type storage node pattern and study on issues relevant to the etching technique. In order to form a concave structure with SiO<sub>2</sub>, we have tried to elevate the SiO<sub>2</sub> to PR etch selectivity. We deposit the protective PR layer and then the etch back is performed to isolate the Pt layer of each concave structure. The height of the remaining PR inside the concave hole is optimized. The relative etch rates of Pt, PR, and SiO<sub>2</sub> are optimized in the Pt etchback process.

# Acknowledgment

This work was supported by INHA UNIVERSITY Research Grant (INHA-22098)

#### References

- K. Tokashiki, K. Saito, K. Takemura, S. Yamamishi, P. Y. Lesaicherre, H. Miyamoto, E. Ikawa, Y. Miyasaka, Proceedings of the 16<sup>th</sup> Dry Process Symposium, Tokyo, 73 (1994).

- 2. S. Saito, K. Juramasu, Jpn. J. Appl. Phys. 31, 135 (1992).

- 3. H. Mace, H. Achard, L. Peccoud, *Microelectronic engineering* 29, 48 (1995).

- 4. J. Baborowski, P. Muralt, N. Ledermann, S. Hiboux, *Vacuum* **56**, 51 (2000).

- D.-S. Wuu, N.-H. Kuo, F.-C. Liao, R.-H. Horng, M.-K. Lee, *Appl. Surf. Sci.* 169-170, 638 (2001).

- K. Nishikawa, Y. Kusumi, T. Oomori, M. Hanazaki, K. Namba. *Jpn. Appl. Phys.* 32, 6102 (1993).

- S. Yokoyama, Y. Ito, K. Ishihara, K. Hamada, S. Ohnishi, J. Kudo, K. Sakiyama. *Jpn. J. Appl. Phys.* 34, 767 (1995).

- W.-J. Yoo, J.-H. Hahm, H.-W. Kim, C.-O. Jung, Y.-B. Koh, M.-Y. Lee, *Jpn. J. Appl. Phys.*, 35, 2501 (1996).

- T. Eimori, Y. Ono, H. Ito, Nikkei Microdevices 2, 99 (1994).

- S. Yokoyama, Y. Ito, K. Ishihara, K. Hamada, S. Ohnishi, J. Kudo, K. Sakiyama, Ext. Abstr. Int. Conf. Solid State Devices Mater, Business Center for Academic Societies, Tokyo, 721 (1994).

- 11. H.-W. Kim, B-S. Ju, C.-J. Kang, J.-T. Moon, Microelectronic Engineering 65, 185 (2003).

- H.-W. Kim, B.-S. Ju, B.-Y. Nam, W.-J. Yoo, C.-J. Kang, T.-H. Ahn, J.-T. Moon, M.-Y. Lee, *J. Vac. Sci. Technol.* A 17, 2151 (1999).